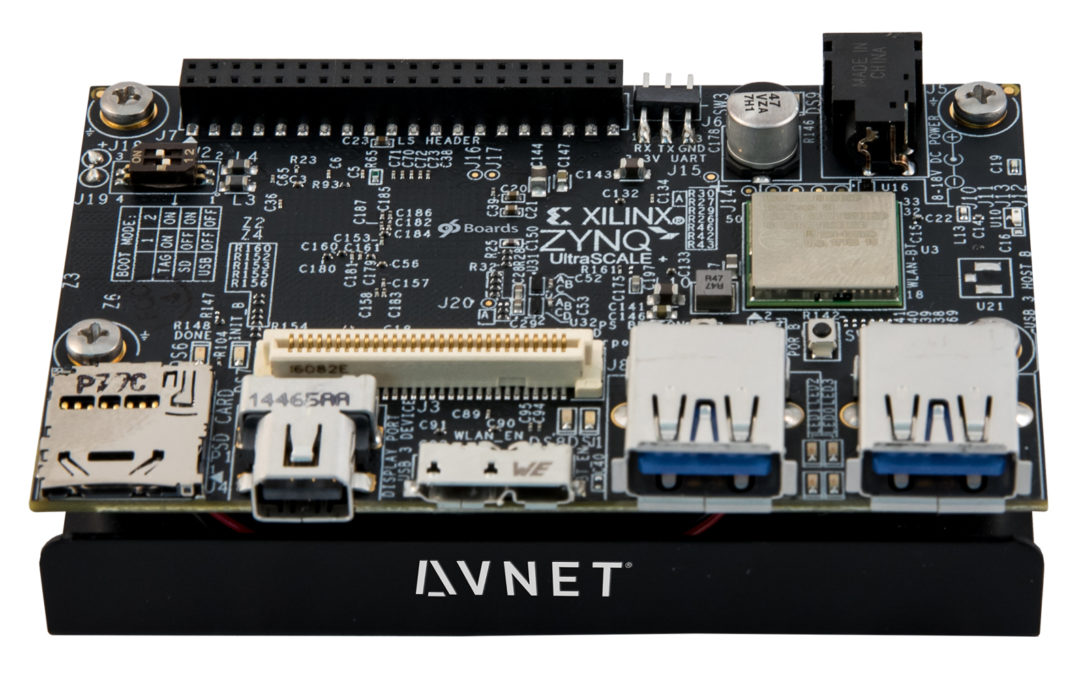

April 02, 2018: Comsis started implementation of Its WiFi IPs on a Xilinx Zynq SoC Eval board supporting a new wideband radio

The new radio comes in the form of an add-on module which plugs into one of the connectors of the Xilinx Zyynq SoC Eval board. The wideband module is based on the AD9361 Agile Radio Transceiver from Analog Devices. It can operate from less than 100 MHz up to 6 GHz, with a tunable channel bandwidth of up to 56 MHz. The excellent performance of the transceiver allows the implementation of very demanding modulations. A single module can be used to implement a 2×2 MIMO scheme, with TDD or FDD duplex modes. More information about the AD9361 Agile Radio Transceiver can be found directly on the website of Analog Devices.

Roxana OJeda, CTO of Comsis, welcomes the new modules:

«There are already many FPGA + wideband radio platforms out there on the market, under a common SDR denomination. A wideband radio is typically attached to a small to medium capacity Xilinx FPGA which does the acquisition and some basic sample-level tasks, and forwards raw data to PC through an USB link. Coupled with the Xilinx Zynq SoC Eval board this opens a whole world of new applications far beyond mere SDR in the lab.»